Architectures des mémoires Flash

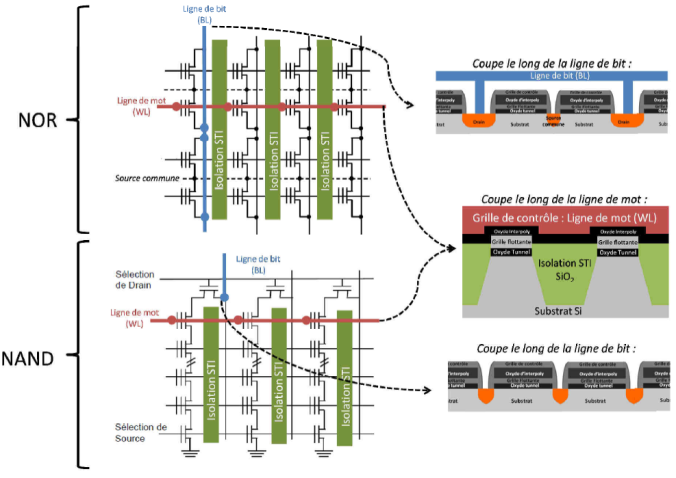

Deux architectures existent, la NAND et la NOR représentées sur la Figure 1. Aucune matrice mémoire n’ayant été utilisée dans ce travail de thèse, nous ne présenterons que brièvement ces architectures et ne rentrerons pas dans les détails de leurs modes de fonctionnement. Ceux-ci sont largement décrits avec beaucoup de précision dans l’ouvrage [Cappelletti99].

Dans l’architecture NOR, les cellules mémoires de chaque ligne ont la grille de contrôle en commun. Les cellules mémoires de chaque colonne ont quant à elles le drain en commun. L’écriture se fait par injection de porteurs chauds, ce qui procure une programmation rapide de chaque cellule, mais assez lente au global car la programmation par bloc n’est pas possible. Cette architecture permet un accès aléatoire et rapide en lecture à chaque cellule de la matrice en sélectionnant sa WL (word line) et sa BL (bit line). C’est une architecture largement employée dans les mémoires embarquées (microprocesseurs, systèmes sur puces) notamment pour le stockage de code où la rapidité d’accès est primordiale.

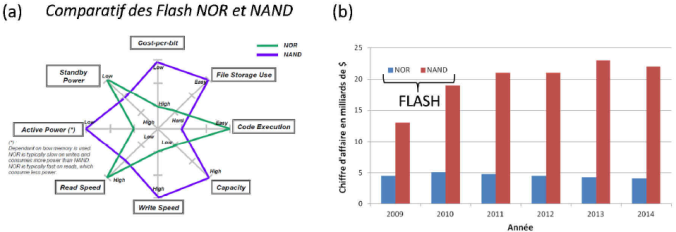

Dans l’architecture NAND, les cellules mémoires de chaque ligne partagent également leur grille de contrôle. Dans chaque colonne, les cellules mémoires sont connectées en série. L’écriture se fait par effet tunnel Fowler-Nordheim. Bien que ce mécanisme de programmation soit plus lent que par injection de porteurs chauds, le fait que la programmation par blocs soit possible rend au final cette architecture plus rapide en écriture que la NOR. Par contre, la lecture d’une cellule se fait en polarisant les autres cellules de la colonne pour qu’elles soient dans l’état conducteur, ce qui augmente le temps d’accès par rapport une NOR à l’accès aléatoire. Cette architecture est plus dense puisqu’elle nécessite moins d’interconnexions que pour la NOR. Elle est donc particulièrement adaptée pour le stockage de masse (« stand-alone ») dans des produits tels que les clés USB, les SSD, les cartes mémoires où la taille est importante. C’est ce qui explique son fort développement ces dernières années, comme décrit sur la Figure 2-a.

L’effacement s’effectue par bloc dans les deux architectures. Le gros avantage est que tous les bits d’une ligne sont effacés en même temps. La rapidité d’effacement procurée par cette architecture est d’ailleurs à l’origine du nom FLASH.

Figure 1 : Schémas électriques et vues en coupe le long des lignes de bit et de mots, des deux architectures mémoires NOR et NAND

Figure 2 : (a) Comparatif des performances électriques des architectures Flash NOR et NAND (b) Evolution du chiffre d’affaire généré par les mémoires Flash NOR et FLASH NAND.[isuppli]